Title: HPC Hardware SDN and BHD: Revolutionizing High Performance Computing

High-performance computing (HPC) has traditionally relied on expensive and powerful servers to process large amounts of data. However, with the rise of software-defined networking (SDN) and block hierarchy design (BHD), HPC can now be run on a variety of hardware platforms without sacrificing performance. SDN allows for more flexible network management and automation, while BHD provides a hierarchical approach to designing and managing HPC systems. By combining these technologies, researchers are able to develop new HPC applications and improve existing ones. For example, SDN can be used to optimize resource allocation in parallel computing environments, while BHD can help manage complex dependencies between different components of an HPC system. As HPC continues to grow in importance for scientific research and other fields, it is likely that we will see further development and refinement of these technologies to support even more demanding applications.

High-performance computing (HPC) has become an indispensable component of various fields, including scientific research, weather forecasting, and drug discovery. However, the complexity and scalability of HPC systems pose significant challenges to their design and management. One of the key aspects that have received increasing attention in recent years is the integration of software-defined networking (SDN) and branch-height decoding (BHD) technologies into HPC hardware architectures. This article aims to provide an overview of HPC hardware SDN and BHD, their potential benefits, and the current state of research in this field.

Software-Defined Networking (SDN) is a network architecture that allows for the virtualization, automation, and programmability of network functions. In traditional computer networks, network devices are typically connected using dedicated physical links or switches. However, in an SDN-enabled network, these devices are interconnected through a central controller that manages the flow of data across the network. The controller acts as a single point of control for all network activities, enabling greater flexibility and scalability compared to traditional network architectures.

In the context of HPC systems, SDN can enable several benefits. First, it provides a flexible and scalable way to manage the complex interconnections between different HPC nodes and resources. By abstracting the underlying network hardware from the applications running on the nodes, SDN can enable more efficient use of network bandwidth and reduce congestion. Second, SDN enables dynamic network configuration and management, allowing administrators to quickly adapt to changing workloads and performance requirements. Finally, SDN can enhance security by providing centralized control over access to critical resources and enabling real-time monitoring and analytics of network activity.

Branch-Height Decoding (BHD) is a technique used by some high-performance computing systems to increase memory bandwidth by selectively reading data from caches based on their height relative to the branch instruction pointer (IP). BHD works by predicting which cache lines will be accessed next and prefetching them into the cache ahead of time. When the prediction is incorrect, the system can read a cache line directly from memory instead of waiting for it to be evicted from the cache due to staleness or conflicts with other data. By reducing memory latency, BHD can improve the performance of HPC applications that rely heavily on memory-intensive operations such as matrix multiplication or neural network training.

Integrating SDN and BHD into HPC hardware architectures requires careful considerations of several factors, including network topology, memory layout, and application behavior. One approach is to use a combination of software-based and hardware-based techniques to implement both SDN and BHD in HPC systems. For example, software-based SDN controllers can be used to manage the network functions, while hardware offload units (HOUs) can perform BHD operations directly on the memory subsystem. Another approach is to adopt a hybrid approach that combines elements of both software-based and hardware-based solutions, depending on the specific requirements of each application or node in the HPC system.

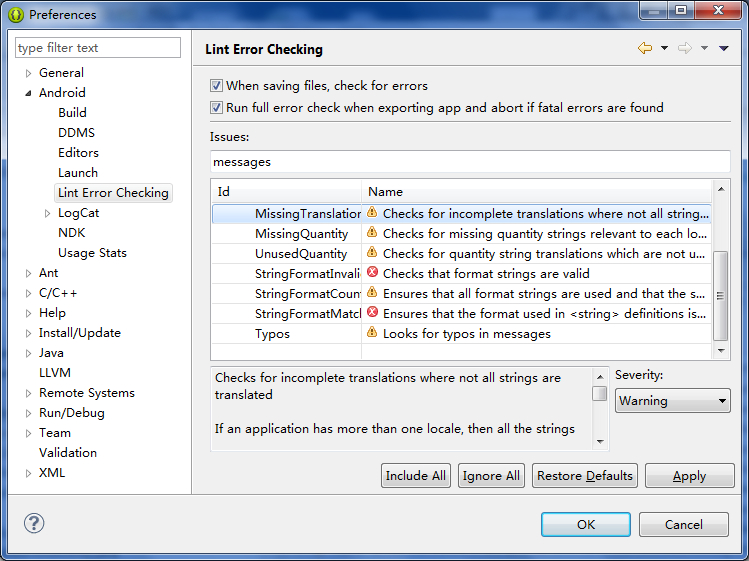

Despite the promising potential of SDN and BHD in HPC systems, there are still several challenges that need to be addressed before they can be widely adopted. One major challenge is the integration of SDN with existing HPC frameworks such as OpenMPI or MPICH. While there are some open-source projects that aim to provide SDN support for HPC platforms (e.g., OpenStack), these solutions often require significant modifications to the underlying frameworks and may not be fully compatible with existing applications. Another challenge is the need for optimized algorithms for BHD that can take advantage of modern memory architectures such as Intel Optane Memory or NVDIMMs. Finally, there is also a need for comprehensive performance evaluation and benchmarking studies to validate the effectiveness of SDN and BHD in HPC environments.

In conclusion, the integration of software-defined networking (SDN) and branch-height decoding (BHD) into high performance computing (HPC) hardware architectures represents a significant opportunity to enhance the scalability, flexibility, and performance of HPC systems. While there are still many challenges that need to be addressed before these technologies can be widely adopted, recent progress in both areas suggests that we are approaching an era where HPC systems can benefit from the same advanced networking capabilities as data center networks. As such, researchers and engineers in the field of HPC should continue to explore new ways to integrate SDN and BHD into HPC hardware architectures, paving the way towards even more powerful and efficient computing systems in the future.

Articles related to the knowledge points of this article:

Altherm Hardware: Revolutionizing the Future of Heating and Cooling

Hulberts Hardware: A Legacy of Quality and Innovation

R. James Hardware: A Legacy of Quality and Innovation

Dazeys Hardware: A Legacy of Quality and Innovation

Title: Enhance the Beauty and Functionality of Your Bathroom with Moen Bathroom Hardware Sets

Title: The Promising Potential of Retained Hardware in Medical Applications